题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

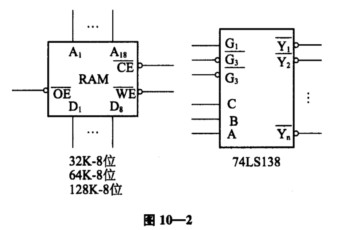

设CPU有18根地址线和8根数据线,并用IO/M(M取反)作访存控制信号,R/W(W取反)作读写命令,存储器采用

设CPU有18根地址线和8根数据线,并用IO/M(M取反)作访存控制信号,R/W(W取反)作读写命令,存储器采用四体低位交叉结构,画出CPU和存储芯片的连接图(见图10—2)。 要求: (1)合理选用下列芯片,门电路自定。 (2)写出每片存储芯片的二进制地址范围。 (3)详细画出存储芯片的片选逻辑。 (4)该存储器在一个存取周期内可向CPU提供多少位信息?

答案

答案

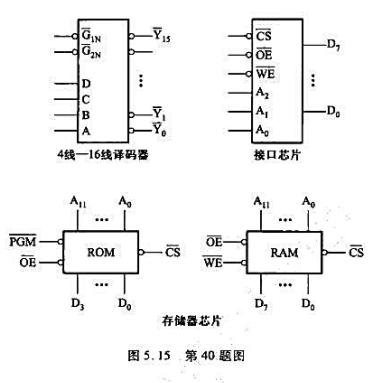

作访存控制信号,

作访存控制信号, 作访问I/0端口的控制信号,

作访问I/0端口的控制信号, 为读命令,

为读命令, 为写命令。I/O编址采用单独编址。现有图5. 15所示的芯片及各种门电路(自定):

为写命令。I/O编址采用单独编址。现有图5. 15所示的芯片及各种门电路(自定):

用作访存控制信号(低电平有效),用

用作访存控制信号(低电平有效),用 作读写控制信号(高电平为读,低电平为写)。现有下列芯片及各种门电路(门电路自定),如图所示。

作读写控制信号(高电平为读,低电平为写)。现有下列芯片及各种门电路(门电路自定),如图所示。

作为访存控制信号(低电平有效),用

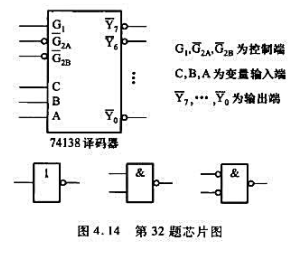

作为访存控制信号(低电平有效),用 作为读/写控制信号(高电平为读,低电平为写)。现有芯片及各种门电路(门电路自定),如图4.15所示。画出CPU与存储器的连接图,要求:

作为读/写控制信号(高电平为读,低电平为写)。现有芯片及各种门电路(门电路自定),如图4.15所示。画出CPU与存储器的连接图,要求:

作为访存控制信号(低电平有效),用

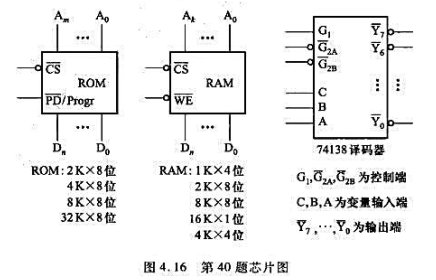

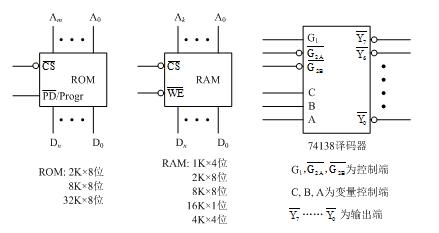

作为访存控制信号(低电平有效),用 作为读/写控制信号(高电平为读,低电平为写)。现有下列存储芯片:1 Kx4位RAM,4Kx8位RAM ,2Kx8位ROM以及74138译码器和各种门电路,如图4.14所示。画出CPU与存储芯片的连接图,要求:

作为读/写控制信号(高电平为读,低电平为写)。现有下列存储芯片:1 Kx4位RAM,4Kx8位RAM ,2Kx8位ROM以及74138译码器和各种门电路,如图4.14所示。画出CPU与存储芯片的连接图,要求:

作为访存控制信号(低电平有效),用

作为访存控制信号(低电平有效),用 作为读/写控制信号(高电平为读,低电平为写)。现有芯片及各种门电路(门电路自定),如图4.16所示。西出CPU与存储器的连接图,要求:

作为读/写控制信号(高电平为读,低电平为写)。现有芯片及各种门电路(门电路自定),如图4.16所示。西出CPU与存储器的连接图,要求: