题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

内部存储器就是CPU能用地址直接寻址的存储器,用来存放将要运行的程序和有关指令。 ()

A.正确

B.错误

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.正确

B.错误

答案

答案

更多“内部存储器就是CPU能用地址直接寻址的存储器,用来存放将要运行的程序和有关指令。 ()”相关的问题

更多“内部存储器就是CPU能用地址直接寻址的存储器,用来存放将要运行的程序和有关指令。 ()”相关的问题

第1题

第2题

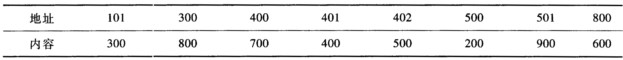

一条双字长的取数指令(LDA)存于存储器的100和101单元,其中第一个字为操作码和寻址特征M,第二个字为形式地址。假设PC当前值为100,变址寄存器XR的内容为100,基址寄存器的内容为200。存储器各单元的内容如下所示:

写出下列寻址方式的有效地址,以及取数指令执行结束后,累加器ACC的内容。 (1)直接寻址 (2)立即寻址 (3)间接寻址 (4)相对寻址 (5)变址寻址 (6)基址寻址

写出下列寻址方式的有效地址,以及取数指令执行结束后,累加器ACC的内容。 (1)直接寻址 (2)立即寻址 (3)间接寻址 (4)相对寻址 (5)变址寻址 (6)基址寻址

第3题

某机主存为64KB,CPU内有8个16位通用寄存器(其中4个又可以当成8个8位通用寄存器)。该机指令系统有64条指令,全部为双地址指令.且必有一个操作数R在寄存器中,另一操作数采用下列寻址方式:

(1)寄存器直接寻址。

(2)寄存器间接寻址(用16位寄存器)。

(3)存储器直接寻址。

(4)变址寻址(用任意一个16位寄存器做变址寄存器.位移量16位)。

要求:

(1)设计该计算机的指令格式.并列出各种类型的指令格式。

(2)写出各种寻址方式的有效地址。

第4题

(1)将Imm16加到寄存器R1中,此时,Imm16为立即操作数,即R[R1]←R[R1]+Imm16。

(2)将存储单元Imm16中的内容加到寄存器R1中,此时,Imm16为直接地址,即

R[R1]←R[R1]+M[mm16]。

(3)将存储单元Imm16中的内容作为地址访问主存,将读出的内容再作为地址访问主存,然后将读出的内容加到寄存器R1中。此时,Imm16为间接地址,即

R[R1]←R[R1]+M[M[Imm16]]。

第5题

某模型机共有64种操作,操作码位数固定,且具有以下特点: (1)采用一地址或二地址格式; (2)有寄存器寻址、直接寻址和相对寻址(位移量为-128~+127)三种寻址方式; (3)有16个通用寄存器,算术运算和逻辑运算的操作数均在寄存器中,结果也在寄存器中; (4)取数/存数指令在通用寄存器和存储器之间传送数据; (5)存储器容量为1 MB,按字节编址。 要求设计算术逻辑指令、取数/存数指令和相对转移指令的格式,并简述理由。

第7题

判断是非并简要说明原因。

(1)如果两种计算机的主频相同,则它们的运算速度也是相同的。

(2)控制存储器中的微指令是由用户设计的。

(3)采用微程序控制器的处理器称为微处理器。

(4)确定下一条微指令地址时。就是用微程序计数器μPC增量(例如μPC+1)来给出该地址的。

(5)RISC计算机采用多种寻址方式和多种指令格式。

(6)RISC机采用循环重叠窗口技术后,使用窗口的子程序嵌套深度可不受限制。

(7)每条指令的第1个机器周期不一定执行取指令操作。

(8)堆栈计算机的指令都是执行压入和弹出操作。

(9)CPU的指令都是以同步控制方式实现的。

(10)可将多个三态门和0C门的输出连到一根导线上。

第8题

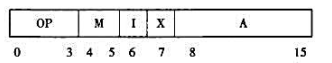

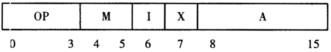

某机存储器容量为64 Kx16位,该机访存指令格式如下:

其中M为寻址模式:0为直接寻址,1为基址寻址,2为相对寻址,3为立即寻址;I为间址特征(I=1间址);X为变址特征(X=1变址)。.

设PC为程序计数器,Rx为变址寄存器,RB为基址寄存器,试问:

(1)该指令能定义多少种操作?

(2)立即寻址操作数的范围。

(3)在非间址情况下,除立即寻址外,写出每种寻址方式计算有效地址的表达式。

(4)设基址寄存器为14位,在非变址直接基址寻址时,指令的寻址范围是多少?

(5)间接寻址时,寻址范围是多少?若允许多重间址,寻址范围又是多少?

第9题

某机存储器容量为64K×16位,该机访存指令格式如下:

其中M为寻址模式:0为直接寻址,1为基址寻址,2为相对寻址,3为立即寻址;I为间址特征(I=1间址);X为变址特征(X=1变址)。 设PC为程序计数器,RX为变址寄存器,RB为基址寄存器,试问: (1)该指令能定义多少种操作? (2)立即寻址操作数的范围。 (3)在非间址情况下,除立即寻址外,写出每种寻址方式计算有效地址的表达式。 (4)设基址寄存器为14位,在非变址直接基址寻址时,指令的寻址范围是多少? (5)间接寻址时,寻址范围是多少?若允许多重间址,寻址范围又是多少?

其中M为寻址模式:0为直接寻址,1为基址寻址,2为相对寻址,3为立即寻址;I为间址特征(I=1间址);X为变址特征(X=1变址)。 设PC为程序计数器,RX为变址寄存器,RB为基址寄存器,试问: (1)该指令能定义多少种操作? (2)立即寻址操作数的范围。 (3)在非间址情况下,除立即寻址外,写出每种寻址方式计算有效地址的表达式。 (4)设基址寄存器为14位,在非变址直接基址寻址时,指令的寻址范围是多少? (5)间接寻址时,寻址范围是多少?若允许多重间址,寻址范围又是多少?

第10题

A.统一编址就是将1/0地址看做是存储器地址的一部分,可用专门的I/O指令对设备进行访问

B.不统一编址是指I/O地址和存储器地址是分开的,所以对I/O访问必须有专门的I/O指令

C.统一编址是指I/O地址和存储器地址是分开的,所以可用访存指令实现CPU对设备的访问