题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

8253定时器计数器的计数基于()原理。

A.减1计数

B.加1计数

C.定时减1,计数加1计数

D.定时加1,计数减1计数

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.减1计数

B.加1计数

C.定时减1,计数加1计数

D.定时加1,计数减1计数

答案

答案

更多“8253定时器计数器的计数基于()原理。”相关的问题

更多“8253定时器计数器的计数基于()原理。”相关的问题

第1题

A.定时时,一个时钟周期加1

B.定时时,一个机器周期加1

C.定时时,一个指令周期加1

D.计数时,上升沿加1

E.计数时,下降沿加1

第2题

8031单片机的定时器T0用作计数方式时是()

A.由内部时钟频率定时,一个时钟周期加1

B.由内部时钟频率定时,一个机器周期加1

C.由外部计数脉冲计数,正跳变加1

D.由外部计数脉冲计数,一个机器周期加1

第3题

A.置输入信号UP/DN=0,则为加1计数;

B.置输入信号UP/DN=0,则为减1计数;

C.Rco仅为进位信号;

D.计数器不能用跳跃的方法实现任意模数的计数。

第8题

中规模时序电路分析设计

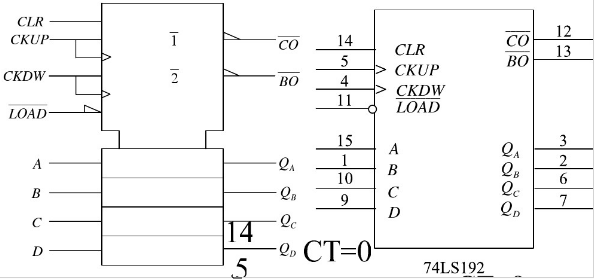

74LS192是十进制计数器,计数的编码采用8421码,计数循环是0000~1001,74LS192是采用双时钟方式的可逆计数器。 是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是

是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是 ,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

| 74LS192的逻辑功能表 | |||||||||||

| CKUP | CKDW | bar{LOAD} | CLR | D | C | B | A | QD | QC | QB | QA |

| varphi | varphi | varphi | 1 | varphi | varphi | varphi | varphi | 0 | 0 | 0 | 0 |

| varphi | varphi | 0 | 0 | d | c | b | a | d | c | b | a |

| ↑ | 1 | 1 | 0 | varphi | varphi | varphi | varphi | 加计数 | |||

| 1 | ↑ | 1 | 0 | varphi | varphi | varphi | varphi | 减计数 | |||

| 1 | 1 | 1 | 0 | varphi | varphi | varphi | varphi | 保持原状态 |

第9题

分别用相关器件和VHDL语言设计一个可控同步计数器,要求:

在M=0时,按加1顺序(0→1→2→…)计数,并实现模5计数器;在M=1时,按加2顺序(0→2→4→1→…)计数,并实现模5计数器。