题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

逻辑分析题 4位同步二进制计数器74161的功能表如表所示,Q3为高位输出,C为与时钟同步的进位输出,进入1111状

逻辑分析题

4位同步二进制计数器74161的功能表如表所示,Q3为高位输出,C为与时钟同步的进位输出,进入1111状态且ENT=1时,由C端输出一个周期的正脉冲。

| CP | R_{bar{D}} | bar{LD} | ENP | ENT | Q3 | Q2 | Q1 | Q0 |

| varphi | 0 | varphi | varphi | varphi | 0 | 0 | 0 | 0 |

| ↑ | 1 | 0 | varphi | varphi | D3 | D2 | D1 | D0 |

| varphi | 1 | 1 | 0 | 1 | 保持 | |||

| varphi | 1 | 1 | varphi | 0 | 保持(但C=0) | |||

| ↑ | 1 | 1 | 1 | 1 | 加法计数 |

答案

答案

分别为进位和借位输出端。

分别为进位和借位输出端。

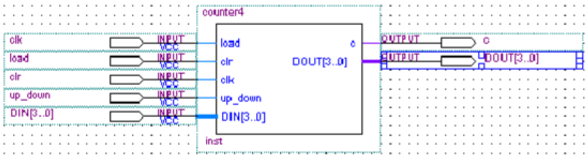

1.jpg) 试求一个Z脉冲周期内应包含多少个CP脉冲周期。

试求一个Z脉冲周期内应包含多少个CP脉冲周期。2.jpg)

是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是

是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是 ,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题: