题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

用PALl6R4设计一个4位二进制可控计数器.要求在控制信号M1M0=11时作加法计数;在M1M

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“用PALl6R4设计一个4位二进制可控计数器.要求在控制信号M1M0=11时作加法计数;在M1M”相关的问题

更多“用PALl6R4设计一个4位二进制可控计数器.要求在控制信号M1M0=11时作加法计数;在M1M”相关的问题

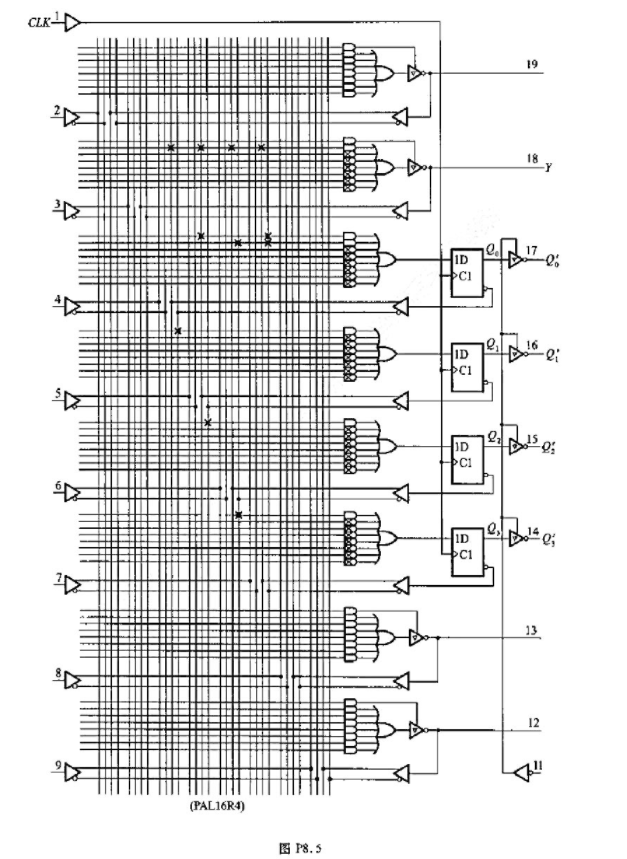

第1题

用PAL16R4设计一个4位二进制可控计数器。要求在控制信号M1M0=11时作加法计数;在M1M0=10时为预置数状态(时钟信号到达时将输入数据D3D2D1D0并行置入4个触发器中);M1M0=01时为保持状态(时钟信号到达时所有触发器保持状态不变);M1M0=00时为复位状态(时钟信号到达时所有的触发器同对被置1)。此外,还应给出进位输出信号。PAL16R4的电路图见图8.5.1。

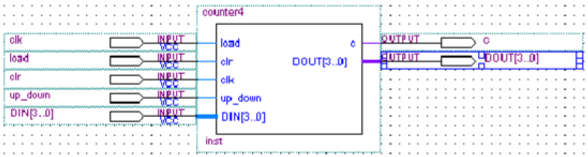

第2题

用一片如图A1-4所示的4位二进制加法计数器74161和必要的逻辑门电路设计一个可控计数器,要求当控制信号M=1时,实现七进制计数器;而当控制信号M=0时,实现十三进制计数器。画出所设计的可控计数器的逻辑电路。

第3题

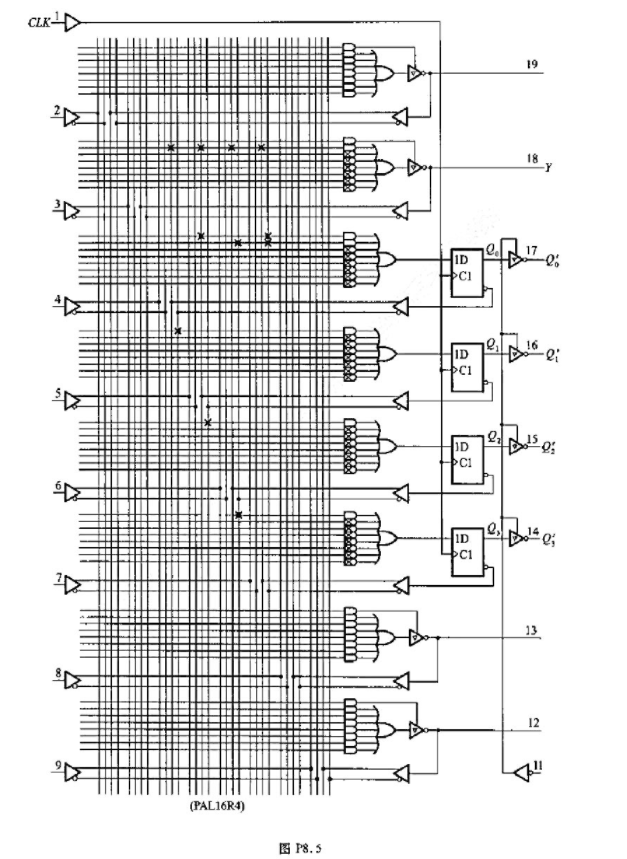

4位二进制加法计数器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4位二进制加法计数器电路,建立4位二进制加法计数器的实验模式。通过电路仿真和硬件验证,进一步了解4位二进制加法计数器的功能和特性。

设计原理

4位二进制加法计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;CLRN是复位输入端,低电平有效;Q[3..0]是计数器的状态输出端;COUT是进位输出端。

第5题

可控计数器,当控制信号C,A等于1和控制信号C,A等于0时,分别实现几进制计数器.

(2)用74161实现91进制计数器.

第6题

用PAL16R6设计一个4位二进制计数器,要求:

(1)具有并行置数功能。并行数据输入为P0,P1,P2,P3,控制信号为

(2)具有加/减计数功能。控制信号为

(3)具有并行输出Q0,Q1,Q2,Q3。

(4)具有进位输出C和借位输出B。

第8题

设计一个可控同步计数器,M1、M2为控制信号,要求:

(1)M1M2=00时,维持原状态;

(2)M1M2=01时,实现模2计数;

(3)M1M2=10时,实现模4计数;

(4)M1M2=11时,实现模8计数。

第9题

设计一个可控进制计数器,当控制输入M=0时为七进制计数,当M=1时为十三进制计数。 (1)试用MSI计数器设计该可控计数器。 (2)用VHDL语言设计该可控计数器。

第10题

用同步二进制加法计数器74161(逻辑符号及功能表见附录)和一个3-8线译码器74138以及门电路设计一个具有开机消零功能的模7计数器,要求计数器按下列规律计数,要求写出设计过程,画出电路图:

0,4,9,12,3,6,9,0,4,…